# LXT974A/LXT975A

## Fast Ethernet 10/100 Quad Transceivers

## **General Description**

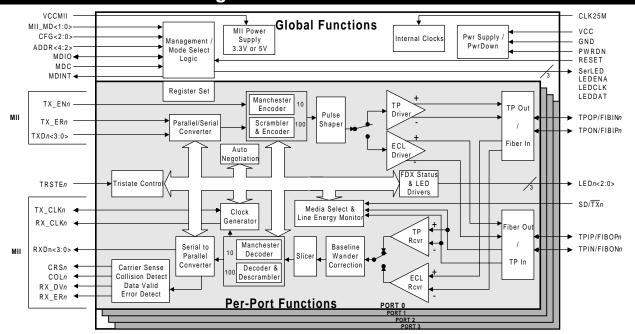

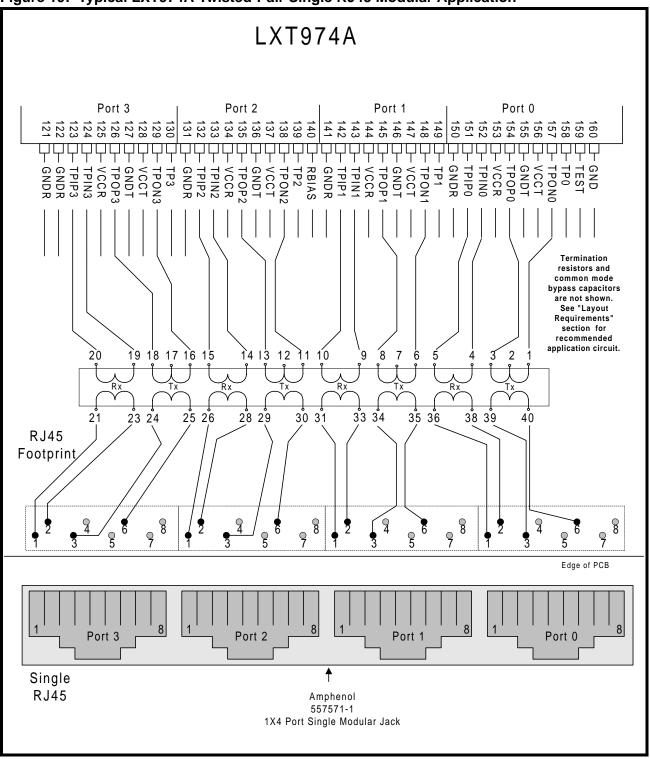

The LXT974A and LXT975A are four-port PHY Fast Ethernet Transceivers which support IEEE 802.3 physical layer applications at both 10 Mbps and 100 Mbps. They provide all of the active circuitry to interface four 802.3 Media Independent Interface (MII) compliant controllers to 10BASE-T and/or 100BASE-TX media. This data sheet applies to all LXT974\_ and LXT975\_ products including LXT974, LXT975 and any subsequent variants, except as specifically noted.

All four ports on the LXT974A provide a combination twisted-pair (TP) or pseudo-ECL (PECL) interface for a 10/100BASE-TX or 100BASE-FX connection.

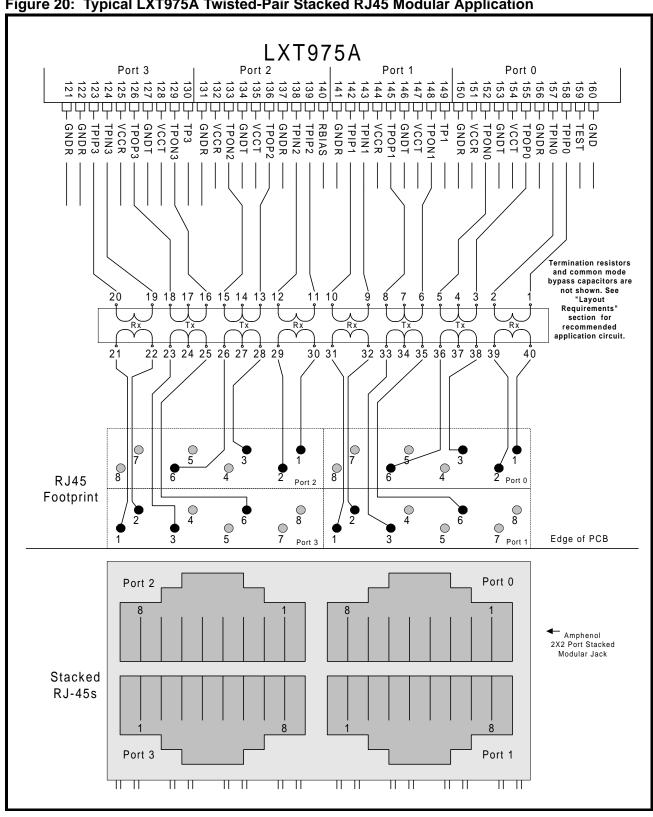

The LXT975A is pin compatible with the LXT974A except for the network ports. The LXT975A is optimized for dual-high stacked RJ45 modular applications and provides a twisted-pair interface on every port, but the PECL interface on only two.

The LXT974A/975A provides three separate LED drivers for each of the four PHY ports and a serial LED interface. In addition to standard Ethernet, each chip supports full-duplex operation at 10 Mbps and 100 Mbps. The LXT974A/975A requires only a single 5V power supply. The MII may be operated independently with either a 3.3V or 5V supply.

### **Features**

- Four independent IEEE 802.3-compliant 10BASE-T or 100BASE-TX ports in a single chip.

- 100BASE-FX fiber-optic capable.

- Standard CSMA/CD or full-duplex operation.

- Supports auto-negotiation and legacy systems without auto-negotiation capability.

- · Baseline wander correction.

- 100BASE-TX line performance over 130 meters.

- Configurable LED drivers and serial LED output.

- Configurable through MII serial port or via external control pins.

- Available in 160-pin PQFP with heat spreader.

- Commercial temperature range (0-70°C ambient).

- Part numbers:

- LXT974AHC (new designation)

- LXT974QC (original designation)

- LXT975AHC (new designation)

- LXT975QC (original designation)

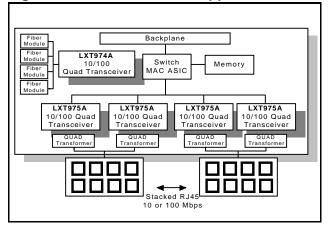

## **Applications**

- 10BASE-T, 10/100-TX, or 100BASE-FX Switches and multi-port NICs.

- LXT975A optimized for dual-high stacked modular RJ45 applications.

## LXT974A/975A Block Diagram

# **TABLE OF CONTENTS**

| PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS         | 4  |

|-------------------------------------------------|----|

| FUNCTIONAL DESCRIPTION                          | 14 |

| Introduction                                    | 14 |

| Network Media/Protocol Support                  | 15 |

| 10/100 Mbps Network Interface                   |    |

| Twisted-Pair Interface                          |    |

| Fiber Interface                                 |    |

| MII Interface                                   | 16 |

| MII Data Interface                              | 16 |

| Loopback                                        | 17 |

| MII Management Interface                        |    |

| MII Interrupts                                  | 18 |

| Hardware Control Interface                      | 19 |

| Initialization                                  | 21 |

| MDIO Control Mode                               | 21 |

| Manual Control Mode                             |    |

| Link Configuration                              | 21 |

| Auto-Negotiation                                | 22 |

| 100 Mbps Operation                              | 23 |

| 4B/5B Coding Table                              | 24 |

| 100BASE-X Protocol Sublayer Operations          | 25 |

| 10 Mbps Operation                               | 28 |

| LED Functions                                   | 29 |

| Serial LED Output                               |    |

| Per-Port LEDs                                   | 29 |

| Operating Requirements                          | 30 |

| Power Requirements                              |    |

| Clock Requirements                              | 30 |

| APPLICATION INFORMATION                         | 31 |

| Design Recommendations                          | 31 |

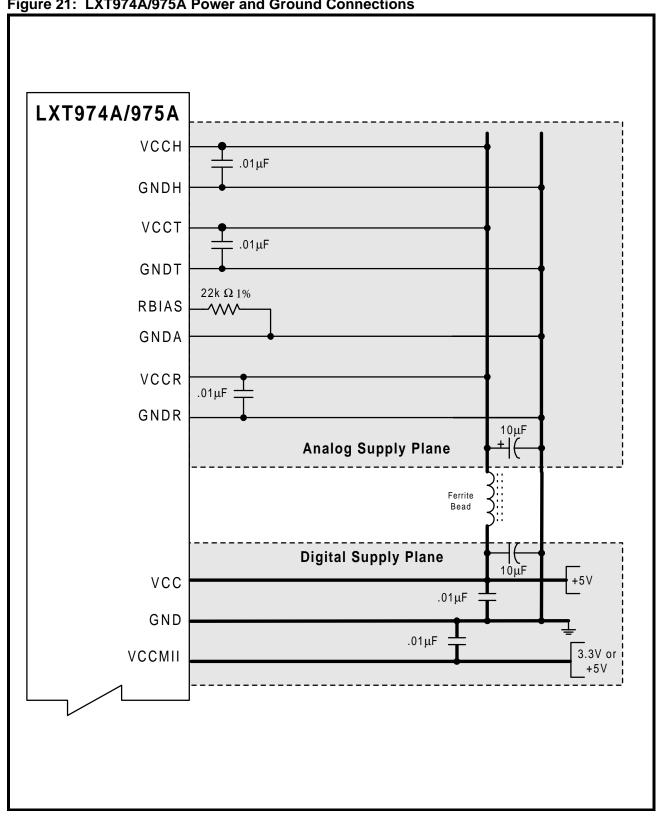

| Power Supply Filtering                          | 31 |

| Power and Ground Plane Layout Considerations    |    |

| Twisted-Pair and Fiber Interfaces               |    |

| Magnetics Information                           |    |

| Magnetics With Improved Return Loss Performance | 34 |

| Typical Application Circuitry                   | 36 |

| TEST SPECIFICATIONS                                        | 42 |

|------------------------------------------------------------|----|

| Absolute Maximum Ratings                                   | 42 |

| Operating Conditions                                       | 42 |

| Digital I/O Characteristics                                | 43 |

| Digital I/O Characteristics - MII Pins                     | 43 |

| Required CLK25M Characteristics                            | 43 |

| Low-Voltage Fault Detect Characteristics                   | 44 |

| 100BASE-TX Transceiver Characteristics                     | 44 |

| 100BASE-FX Transceiver Characteristics                     | 45 |

| 10BASE-T Transceiver Characteristics                       | 45 |

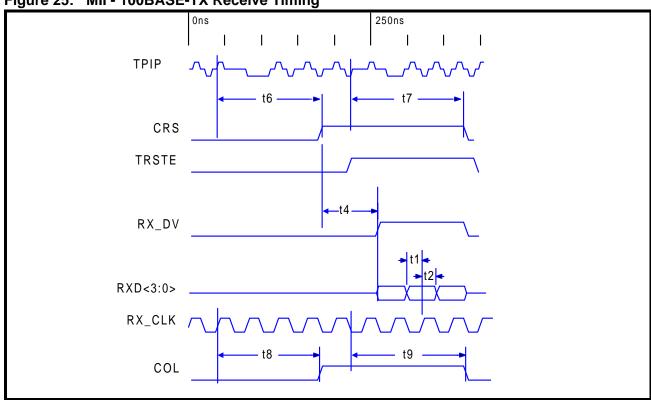

| MII-100BASE-TX Receive Timing                              | 46 |

| MII-100BASE-TX Transmit Timing                             | 47 |

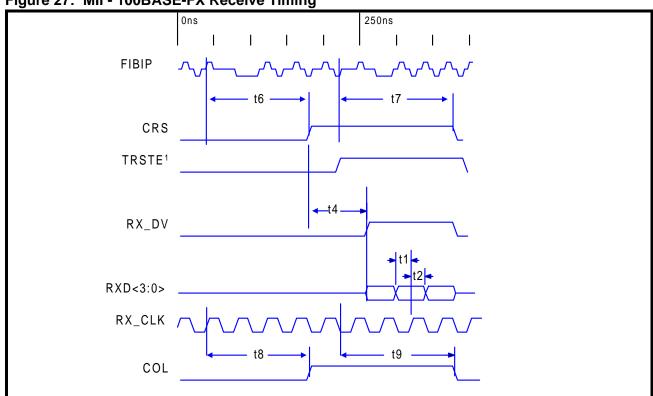

| MII-100BASE-FX Receive Timing                              | 48 |

| MII-100BASE-FX Transmit Timing                             | 49 |

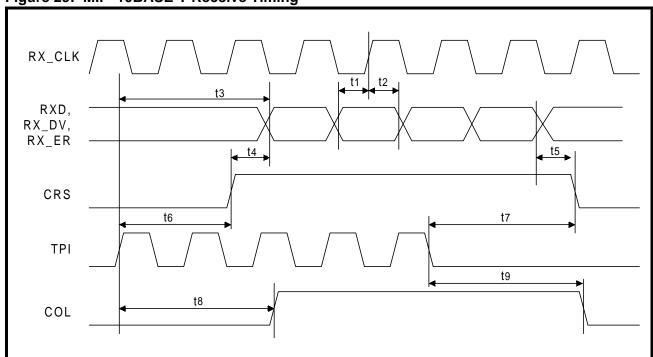

| MII-10BASE-T Receive Timing                                | 50 |

| MII-10BASE-T Transmit Timing                               | 51 |

| 10BASE-T SQE (Heartbeat) Timing                            | 52 |

| 10BASE-T Jab and Unjab Timing                              | 52 |

| Auto Negotiation and Fast Link Pulse Timing                | 53 |

| MDIO and MII Timing                                        | 54 |

| Reset and Power-Down Recovery Timing                       | 55 |

| Serial LED Timing                                          | 55 |

| REGISTER DEFINITIONS                                       | 56 |

| Control Register (Address 0)                               | 57 |

| Status Register (Address 1)                                | 58 |

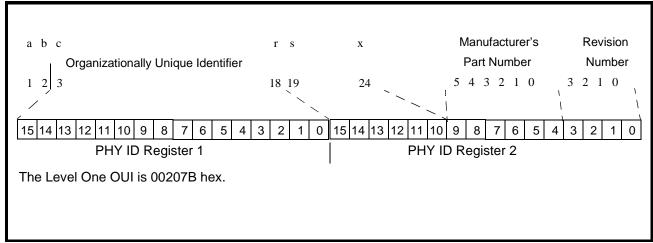

| PHY Identification Register 1 (Address 2)                  | 59 |

| PHY Identification Register 2 (Address 3)                  | 59 |

| Auto Negotiation Advertisement Register (Address 4)        | 60 |

| Auto Negotiation Link Partner Ability Register (Address 5) | 61 |

| Auto Negotiation Expansion (Address 6)                     | 62 |

| LED Configuration Register (Address 16, hex 10)            | 63 |

| Interrupt Enable Register (Address 17, hex 11)             | 64 |

| Interrupt Status Register (Address 18, hex 12)             | 64 |

| Port Configuration Register (Address 19, hex 13)           | 65 |

| Port Status Register (Address 20, hex 14)                  | 66 |

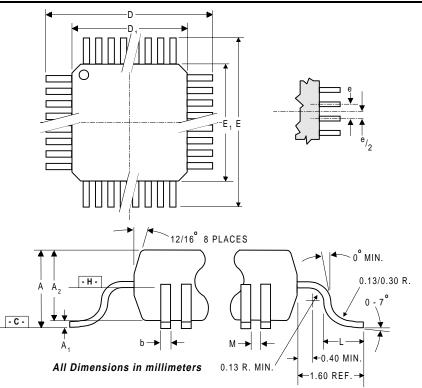

| PACKAGE SPECIFICATION                                      | 67 |

| REVISION HISTORY                                           | 68 |

## PIN ASSIGNMENTS AND SIGNAL DESCRIPTIONS

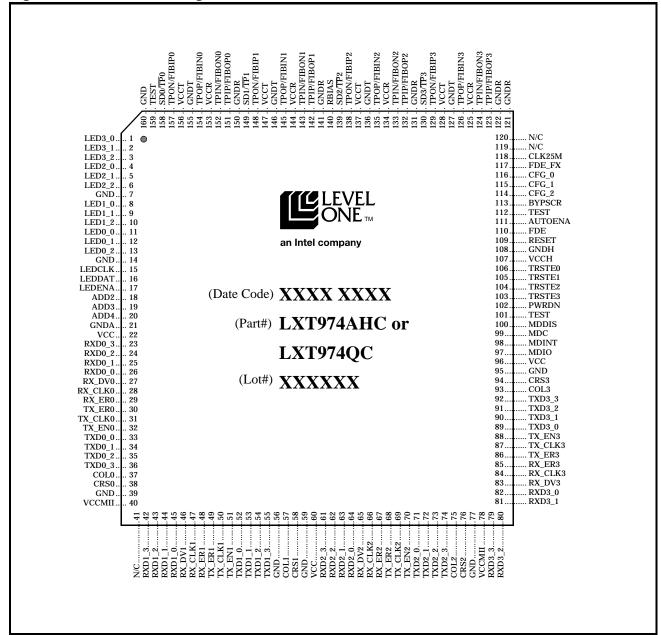

Figure 1: LXT974 Pin Assignments

Table 1: LXT974A Signal Detect/TP Select Signal Descriptions

| Pin# <sup>2</sup>        | Symbol                                   | Type <sup>1</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 158<br>149<br>139<br>130 | SD0/TP0<br>SD1/TP1<br>SD2/TP2<br>SD3/TP3 | I                 | Signal Detect - Ports 0 - 3. When SD/TPn pins are tied High or to a 5V PECL input, bit 19.2 = 1 and the operating mode of each respective port is forced to FX mode. In this mode, full-duplex is set via pin 117 (FDE_FX). When not using FX mode, SD/TPn pins should be tied to GNDT.  TP Select - Ports 0 - 3. When SD/TPn pins are tied Low, bit 19.2 = 0. The operating mode of each port can be set to 10BASE-T, 100BASE-TX, or 100BASE-FX via the hardware control interface pins as show (CFE at ASSE |

|                          |                                          |                   | Note: Hardware control interface pins (CFG_0, CFG_1, CFG_2, FDE, BYPSCR, and AUTOENA) are global and set all ports simultaneously.  In TP mode, network pins operate as described in Table 2.  In FX mode, network pins are re-mapped and operate as described in Table 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

$<sup>1. \ \ \, \</sup>text{Type Column Coding: I} = \text{Input, O} = \text{Output.}$

Table 2: LXT974A Twisted-Pair Interface Signal Descriptions

| Pin#                                          | Symbol                                                       | Type <sup>1</sup> | Signal Description                                                                                                                                                          |  |

|-----------------------------------------------|--------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

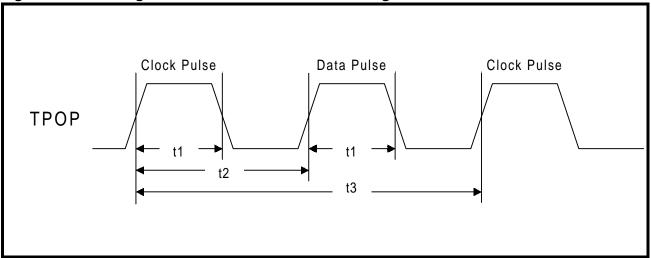

| 154, 157<br>145, 148<br>135, 138<br>126, 129  | TPOP0, TPON0<br>TPOP1, TPON1<br>TPOP2, TPON2<br>TPOP3, TPON3 | O                 | Twisted-Pair Outputs, Positive & Negative - Ports 0-3.  During 100BASE-TX or 10BASE-T operation, TPO pins drive 802.3 compliant pulses onto the line.                       |  |

| 151, 152<br>142, 143<br>132, 133<br>123, 124  | TPIP0, TPIN0<br>TPIP1, TPIN1<br>TPIP2, TPIN2<br>TPIP3, TPIN3 | Ι                 | Twisted-Pair Inputs, Positive & Negative - Ports 0-3.  During 100BASE-TX or 10BASE-T operation, TPI pins receive differential 100BASE-TX or 10BASE-T signals from the line. |  |

| 1. Type Column Coding: I = Input, O = Output. |                                                              |                   |                                                                                                                                                                             |  |

**Table 3: LXT974A Fiber Interface Signal Descriptions**

| Pin#                                         | Symbol                                                               | Type <sup>1</sup> | Signal Description                                                                                                                                |

|----------------------------------------------|----------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 154, 157<br>145, 148<br>135, 138<br>126, 129 | FIBINO, FIBIPO<br>FIBIN1, FIBIP1<br>FIBIN2, FIBIP2<br>FIBIN3, FIBIP3 | I                 | Fiber Inputs, Positive & Negative - Ports 0-3.  During 100BASE-FX operation, FIBI pins receive differential PECL inputs from fiber transceivers.  |

| 151, 152<br>142, 143<br>132, 133<br>123, 124 | FIBOP0, FIBON0<br>FIBOP1, FIBON1<br>FIBOP2, FIBON2<br>FIBOP3, FIBON3 | O                 | Fiber Outputs, Positive & Negative - Ports 0-3.  During 100BASE-FX operation, FIBO pins produce differential PECL outputs for fiber transceivers. |

<sup>1.</sup> Type Column Coding: I = Input, O = Output.

<sup>2.</sup> When not using fiber mode, SD/TPn pins should be tied to GNDT.

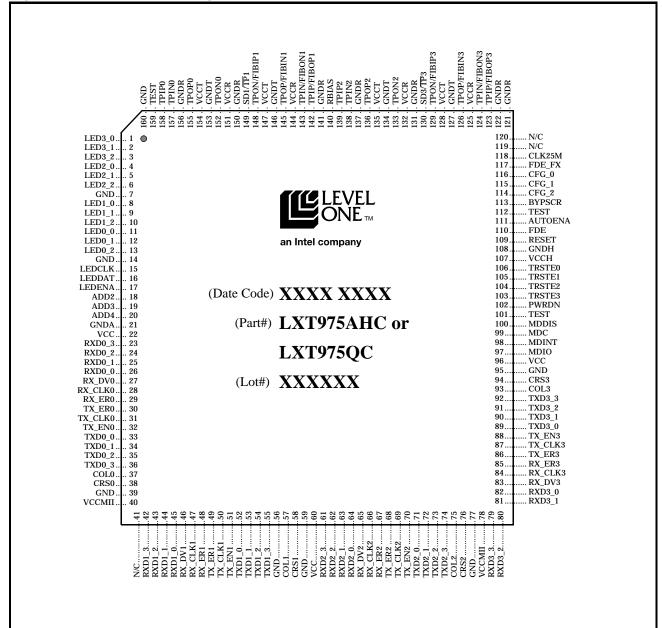

Figure 2: LXT975A Pin Assignments

Table 4: LXT975A Signal Detect/TP Select Signal Descriptions

| Pin# <sup>2</sup> | Symbol             | Type <sup>1</sup> | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 149<br>130        | SD1/TPI<br>SD3/TP3 | I                 | <b>Signal Detect - Ports 1 &amp; 3</b> . When SD/TP <i>n</i> pins are tied High or to a 5V PECL input, bit 19.2 = 1 and the operating mode of each respective port is forced to FX mode. In this mode, full-duplex is set via pin 117 (FDE_FX). When not using fiber mode, SD/TP <i>n</i> pins should be tied to GNDT.                                                                                                                                                                                                       |

|                   |                    |                   | <b>TP Select - Ports 1 &amp; 3</b> . When SD/TP <i>n</i> pins are tied Low, bit 19.2 = 0. The operating mode of each port can be set to 10BASE-T, 100BASE-TX, or 100BASE-FX via the hardware control interface pins as shown in Table 8 on page 11. Note: Hardware control interface pins (CFG_0, CFG_1, CFG_2, FDE, BYPSCR, and AUTOENA) are global and set all ports simultaneously. In TP mode, network pins operate as described in Table 5. In FX mode, network pins are re-mapped and operate as described in Table 6. |

<sup>1.</sup> Type Column Coding: I = Input, O = Output.

**Table 5: LXT975A Twisted-Pair Interface Signal Descriptions**

| Pin#        | Symbol                                        | Type <sup>1</sup> | Signal Description                                            |  |

|-------------|-----------------------------------------------|-------------------|---------------------------------------------------------------|--|

| 155, 152    | TPOP0, TPON0                                  | О                 | Twisted-Pair Outputs, Positive & Negative - Ports 0-3.        |  |

| 145, 148    | TPOP1, TPON1                                  |                   | During 100BASE-TX or 10BASE-T operation, TPO pins drive 802.3 |  |

| 136, 133    | TPOP2, TPON2                                  |                   | compliant pulses onto the line.                               |  |

| 126, 129    | TPOP3, TPON3                                  |                   |                                                               |  |

| 158, 157    | TPIP0, TPIN0                                  | I                 | Twisted-Pair Inputs, Positive & Negative - Ports 0-3.         |  |

| 142, 143    | TPIP1, TPIN1                                  |                   | During 100BASE-TX or 10BASE-T operation, TPI pins receive     |  |

| 139, 138    | TPIP2, TPIN2                                  |                   | differential 100BASE-TX or 10BASE-T signals from the line.    |  |

| 123, 124    | TPIP3, TPIN3                                  |                   |                                                               |  |

| Type Column | 1. Type Column Coding: I = Input, O = Output. |                   |                                                               |  |

**Table 6: LXT975A Fiber Interface Signal Descriptions**

| Pin#           | Symbol                                     | Type <sup>1</sup> | Signal Description                                                                               |  |

|----------------|--------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|--|

| 145, 148       | FIBIN1, FIBIP1                             | I                 | Fiber Network Interface - Ports 1 and 3                                                          |  |

| 126, 129       | FIBIN3, FIBIP3                             |                   | During 100BASE-FX operation, FIBI pins receive differential PECL inputs from fiber transceivers. |  |

| 142, 143       | FIBOP1, FIBON1                             | О                 | Fiber Network Interface - Ports 1 and 3                                                          |  |

| 123, 124       | FIBOP3, FIBON3                             |                   | During 100BASE-FX operation, FIBO pins produce differential PECL outputs for fiber transceivers. |  |

| 1. Type Column | Type Column Coding: I = Input, O = Output. |                   |                                                                                                  |  |

<sup>2.</sup> When not using fiber mode, SD/TPn pins should be tied to GNDT.

Table 7: LXT974A and LXT975A MII Signal Descriptions

| Pin# <sup>3</sup>       | Symbol           | Type <sup>1</sup> | Signal Description <sup>2</sup>                                                                                                                                |  |  |

|-------------------------|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         |                  | .,,,,,            |                                                                                                                                                                |  |  |

| MII Data Interface Pins |                  |                   |                                                                                                                                                                |  |  |

| 33                      | TXD0_0           | I                 | <b>Transmit Data - Port 0</b> . Inputs containing NRZ data to be transmitted from port 0.                                                                      |  |  |

| 34                      | TXD0_1           |                   |                                                                                                                                                                |  |  |

| 35<br>36                | TXD0_2<br>TXD0_3 |                   |                                                                                                                                                                |  |  |

| 52                      | TXD1_0           | I                 | <b>Transmit Data - Port 1</b> . Inputs containing NRZ data to be transmitted from port 1.                                                                      |  |  |

| 53                      | TXD1_0           | 1                 | Transmit Data - 1 or 1. Inputs containing 1442 data to be transmitted from port 1.                                                                             |  |  |

| 54                      | TXD1_2           |                   |                                                                                                                                                                |  |  |

| 55                      | TXD1_3           |                   |                                                                                                                                                                |  |  |

| 71                      | TXD2_0           | I                 | <b>Transmit Data - Port 2</b> . Inputs containing NRZ data to be transmitted from port 2.                                                                      |  |  |

| 72<br>73                | TXD2_1<br>TXD2_2 |                   |                                                                                                                                                                |  |  |

| 74                      | TXD2_2<br>TXD2_3 |                   |                                                                                                                                                                |  |  |

| 89                      | TXD3_0           | I                 | <b>Transmit Data - Port 3.</b> Inputs containing NRZ data to be transmitted from port 3.                                                                       |  |  |

| 90                      | TXD3_1           |                   |                                                                                                                                                                |  |  |

| 91                      | TXD3_2           |                   |                                                                                                                                                                |  |  |

| 92                      | TXD3_3           |                   |                                                                                                                                                                |  |  |

| 32                      | TX_EN0           | I                 | <b>Transmit Enable - Ports 0 - 3.</b> Active High input enables respective port transmitter.                                                                   |  |  |

| 51<br>70                | TX_EN1<br>TX_EN2 |                   | This signal must be synchronous to the TX_CLK.                                                                                                                 |  |  |

| 88                      | TX_EN3           |                   |                                                                                                                                                                |  |  |

| 31                      | TX_CLK0          | О                 | <b>Transmit Clock - Ports 0 - 3</b> . 25 MHz for 100 Mbps operation, 2.5 MHz for 10 Mbps                                                                       |  |  |

| 50                      | TX_CLK1          |                   | operation. The transmit data and control signals must always be synchronized to                                                                                |  |  |

| 69                      | TX_CLK2          |                   | TX_CLK by the MAC. The LXT974A/975A normally samples these signals on the                                                                                      |  |  |

| 87                      | TX_CLK3          |                   | rising edge of TX_CLK. However, Advanced TX_CLK Mode is available by setting MII register bit 19.5=1. In this mode, the LXT974A/975A samples the transmit data |  |  |

|                         |                  |                   | and control signals on the falling edge of TX_CLK.                                                                                                             |  |  |

|                         |                  |                   |                                                                                                                                                                |  |  |

| 30                      | TX_ER0           | I                 | <b>Transmit Coding Error - Ports 0 - 3</b> . This signal must be driven synchronously to                                                                       |  |  |

| 49                      | TX_ER1           |                   | TX_CLK. When High, forces the respective port to transmit Halt (H) code group.                                                                                 |  |  |

| 68<br>86                | TX_ER2           |                   |                                                                                                                                                                |  |  |

| 86                      | TX_ER3           |                   |                                                                                                                                                                |  |  |

Type Column Coding: I = Input, O = Output, OD = Open Drain

The LXT974A/975A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

<sup>3.</sup> Unused pins should be tied Low.

Table 7: LXT974A and LXT975A MII Signal Descriptions - continued

| Table 1           | . LAISIAA          | allu LA           | 1975A WIII Signal Descriptions - continued                                                              |

|-------------------|--------------------|-------------------|---------------------------------------------------------------------------------------------------------|

| Pin# <sup>3</sup> | Symbol             | Type <sup>1</sup> | Signal Description <sup>2</sup>                                                                         |

| 26                | RXD0_0             | О                 | Receive Data - Port 0. Receive data signals (4-bit parallel nibbles) are driven                         |

| 25                | RXD0_1             |                   | synchronously to RX_CLK0.                                                                               |

| 24                | RXD0_2             |                   |                                                                                                         |

| 23                | RXD0_3             |                   |                                                                                                         |

| 45                | RXD1_0             | О                 | Receive Data - Port 1. Receive data signals (4-bit parallel nibbles) are driven                         |

| 44                | RXD1_1             |                   | synchronously to RX_CLK1.                                                                               |

| 43                | RXD1_2             |                   |                                                                                                         |

| 42                | RXD1_3             |                   |                                                                                                         |

| 64                | RXD2_0             | О                 | Receive Data - Port 2. Receive data signals (4-bit parallel nibbles) are driven                         |

| 63                | RXD2_1             |                   | synchronously to RX_CLK2.                                                                               |

| 62                | RXD2_2             |                   |                                                                                                         |

| 61                | RXD2_3             |                   |                                                                                                         |

| 82                | RXD3_0             | О                 | Receive Data - Port 3. Receive data signals (4-bit parallel nibbles) are driven                         |

| 81                | RXD3_1             |                   | synchronously to RX_CLK3.                                                                               |

| 80<br>79          | RXD3_2             |                   |                                                                                                         |

|                   | RXD3_3             |                   |                                                                                                         |

| 27                | RX_DV0             | О                 | Receive Data Valid - Ports 0 - 3. These signals are synchronous to the respective                       |

| 46                | RX_DV1             |                   | RX_CLKn. Active High indication that received code group maps to valid data.                            |

| 65<br>83          | RX_DV2<br>RX_DV3   |                   |                                                                                                         |

|                   |                    |                   | P 1 P 1 A 2 M 1 1 m m l m m d d m m m d m                                                               |

| 29<br>48          | RX_ER0<br>RX_ER1   | О                 | Receive Error - Ports 0 - 3. These signals are synchronous to the respective                            |

| 48<br>67          | RX_ER1<br>RX_ER2   |                   | RX_CLK <i>n</i> . Active High indicates that received code group is invalid, or that PLL is not locked. |

| 85                | RX_ER2<br>RX_ER3   |                   | not rocked.                                                                                             |

| 28                | RX_CLK0            | О                 | Receive Clock - Ports 0 - 3. 25 MHz for 100 Mbps and 2.5 MHz for 10 Mbps.                               |

| 28<br>47          | RX_CLK0<br>RX_CLK1 | U                 | Receive Clock - Ports 0 - 5. 23 IVITIZ 101 100 IVIOPS and 2.3 IVITIZ 101 10 IVIOPS.                     |

| 66                | RX_CLK1            |                   |                                                                                                         |

| 84                | RX_CLK3            |                   |                                                                                                         |

| 37                | COL0               | О                 | Collision Detected - Ports 0 - 3. Active High outputs asserted upon detection of a                      |

| 57                | COL1               |                   | collision. Remain High for the duration of the collision. These signals are generated                   |

| 75                | COL2               |                   | asynchronously. Inactive during full-duplex operation.                                                  |

| 93                | COL3               |                   |                                                                                                         |

| 38                | CRS0               | 0                 | Carrier Sense - Ports 0 - 3. Active High signals. During half-duplex operation                          |

| 58                | CRS1               |                   | (bit $0.8 = 0$ ), CRSn is asserted when either transmit or receive medium is non-idle.                  |

| 76                | CRS2               |                   | During full-duplex operation (bit $0.8 = 1$ ), CRSn is asserted only when the receive                   |

| 94                | CRS3               |                   | medium is non-idle.                                                                                     |

|                   |                    |                   |                                                                                                         |

<sup>1.</sup> Type Column Coding: I = Input, O = Output, OD = Open Drain

<sup>2.</sup> The LXT974A/975A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

<sup>3.</sup> Unused pins should be tied Low.

Table 7: LXT974A and LXT975A MII Signal Descriptions - continued

| Pin# <sup>3</sup>        | Symbol                               | Type <sup>1</sup> | Signal Description <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------------------|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                          | MII Control Interface Pins           |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 97                       | MDIO                                 | I/O               | Management Data Input/Output. Bidirectional serial data channel for PHY/STA communication.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 98                       | MDINT                                | OD                | Management Data Interrupt. An active Low output on this pin indicates status change. Interrupt is cleared by sequentially reading Register 1, then Register 18.                                                                                                                                                                                                                                                                   |  |  |  |

| 99                       | MDC                                  | I                 | Management Data Clock. Clock for the MDIO serial data channel.  Maximum frequency is 2.5 MHz.                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 100                      | MDDIS                                | I                 | Management Disable.  When MDDIS is High, the MDIO is restricted to Read Only and the Hardware Control Interface pins provide continual control of their respective bits.  When MDDIS is Low at power up or Reset, the Hardware Control Interface pins control only the initial or "default" values of their respective register bits. After the power-up/reset cycle is complete, bit control reverts to the MDIO serial channel. |  |  |  |

| 106<br>105<br>104<br>103 | TRSTE0<br>TRSTE1<br>TRSTE2<br>TRSTE3 | I                 | Tristate - Ports 0 - 3. This bit controls bit 0.10 (Isolate bit). When TRSTE <i>n</i> is High, the respective port isolates itself from the MII Data Interface.  When MDDIS is High, TRSTE provides continuous control over bit 0.10.  When MDDIS is Low, TRSTE sets the initial (default) value of bit 0.10 at Reset and then bit control reverts back to the MDIO interface.                                                    |  |  |  |

<sup>1.</sup> Type Column Coding: I = Input, O = Output, OD = Open Drain

<sup>2.</sup> The LXT974A/975A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

<sup>3.</sup> Unused pins should be tied Low.

Table 8: LXT974A and LXT975A Hardware Control Interface Signal Descriptions

|      |                     |                   | 1975A Hardware Control Interface Signal Descriptions                                                                                                                                                                                      |

|------|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin# | Symbol              | Type <sup>1</sup> | Signal Description <sup>2</sup>                                                                                                                                                                                                           |

| 116  | CFG_0<br>(Global)   | I                 | <b>Configuration Control 0. When A/N is enabled,</b> Low to High transition on CFG_0 causes auto-negotiate to restart on all ports and $0.9 = 1$ .                                                                                        |

|      |                     |                   | When A/N is disabled, this input selects operating speed and directly affects bit 0.13.                                                                                                                                                   |

|      |                     |                   | When CFG_0 is High, 100 Mbps is selected and bit $0.13 = 1$ .                                                                                                                                                                             |

|      |                     |                   | When CFG_0 is Low, 10 Mbps is selected and bit $0.13 = 0$ .                                                                                                                                                                               |

| 115  | CFG_1<br>(Global)   | I                 | Configuration Control 1.  When A/N is enabled, CFG_1 determines operating speed advertisement capabilities in combination with CFG_2 and FDE on all ports. See Table 16 on page 19 for details.                                           |

|      |                     |                   | When A/N is disabled, CFG_1 enables 10 Mbps link test and directly affects bit 19.8.                                                                                                                                                      |

|      |                     |                   | When CFG_1 is High, 10 Mbps link test is disabled and bit 19.8 = 1.                                                                                                                                                                       |

|      |                     |                   | When CFG_1 is Low, 10 Mbps link test is enabled and bit 19.8 = 0.                                                                                                                                                                         |

| 114  | CFG_2<br>(Global)   | Ι                 | Configuration Control 2.  When A/N is enabled, CFG_2 determines operating speed advertisement capabilities in combination with CFG_1 on all ports. See Table 16 on page 19 for details.                                                   |

|      |                     |                   | <b>When A/N is disabled</b> , this input selects either TP or FX interface. When FX interface is selected, the LXT974A/975A will automatically disable the scrambler. For correct FX operation, 100 Mbps operation must also be selected. |

|      |                     |                   | Note: It is recommended to set the network interface for each port independently, via the SD/TPn pins. See Tables 1 and 4 for Signal Detect / TP Select signal descriptions and operation.                                                |

|      |                     |                   | When CFG_2 is Low, TP is enabled and bit $19.2 = 0$ .                                                                                                                                                                                     |

|      |                     |                   | When CFG_2 is High, FX is enabled and bit 19.2 = 1.                                                                                                                                                                                       |

| 110  | FDE<br>(Global)     | Ι                 | Full-Duplex Enable - All Ports. When High, enables full-duplex operation on all ports.                                                                                                                                                    |

| 117  | FDE_FX              | Ι                 | Full-Duplex Enable - FX Ports only.  When High, enables full-duplex operation on all ports set for FX mode operation.  This pin is ignored on ports set for TP mode.                                                                      |

| 113  | BYPSCR<br>(Global)  | I                 | Bypass Scrambler. In TP mode, enables or bypasses Scrambler operation and directly affects MDIO register bit 19.3. When High, Scrambler is bypassed and bit 19.3 = 1.                                                                     |

|      |                     |                   | When Low, Scrambler is enabled and bit $19.3 = 0$ .                                                                                                                                                                                       |

|      |                     |                   | <b>In FX mode</b> , the LXT974A/975A_ <i>automatically</i> bypasses the Scrambler. This pin has no effect selecting Scrambler bypass.                                                                                                     |

| 111  | AUTOENA<br>(Global) | I                 | Auto-Negotiation Enable. When High, enables auto-negotiation on all ports.                                                                                                                                                                |

<sup>1.</sup> Type Column Coding: I = Input, O = Output, OD = Open Drain.

<sup>2.</sup> The LXT974A/975A/975\_ supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

Table 9: LXT974A and LXT975A Miscellaneous Signal Descriptions

| Pin#          | Symbol | Type <sup>1</sup> | Signal Description <sup>2</sup>                                                                                                                                               |            |           |               |  |  |  |  |  |

|---------------|--------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|---------------|--|--|--|--|--|

| 20            | ADD4   | I                 | Address <4:2>. Set upper three bits of PHY                                                                                                                                    | ADD1       | ADD0      | Port          |  |  |  |  |  |

| 19            | ADD3   | I                 | address. ADD<1:0> are set internally to                                                                                                                                       | 0          | 0         | 0             |  |  |  |  |  |

| 18            | ADD2   | I                 | match port number as shown at right.                                                                                                                                          | 0          | 1         | 1             |  |  |  |  |  |

|               |        |                   |                                                                                                                                                                               | 1          | 0         | 2             |  |  |  |  |  |

|               |        |                   |                                                                                                                                                                               | 1          | 1         | 3             |  |  |  |  |  |

| 101, 112, 159 | TEST   | I                 | Test. Must be tied Low.                                                                                                                                                       |            |           |               |  |  |  |  |  |

| 140           | RBIAS  | I                 | <b>Bias</b> . This pin provides bias current for the integround through a 22 k $\Omega$ resistor.                                                                             | ernal circ | uitry. Mu | st be tied to |  |  |  |  |  |

| 118           | CLK25M | I                 | Clock Input. A 25 MHz clock input is require tional Description for detailed clock requirements.                                                                              |            | pin. Refe | er to Func-   |  |  |  |  |  |

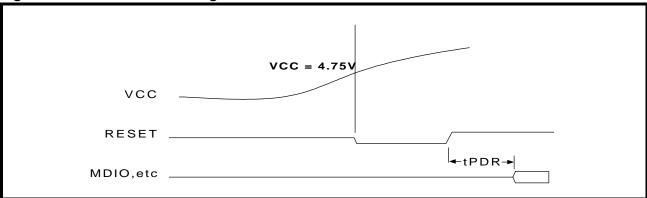

| 109           | RESET  | I                 | <b>Reset</b> . This active Low input is OR'ed with the (0.15). The LXT974A/975A reset cycle is extracted Reset is de-asserted.                                                |            | -         |               |  |  |  |  |  |

| 102           | PWRDN  | I                 | <b>Power Down</b> . When High, forces LXT974A/975A into power down mode. This pin is OR'ed with the Power Down bit (0.11). Refer to Table 44 on page 56 for more information. |            |           |               |  |  |  |  |  |

| 41, 119, 120  | N/C    | -                 | No Connection. Leave open.                                                                                                                                                    |            |           |               |  |  |  |  |  |

$<sup>1. \ \ \, \</sup>text{Type Column Coding: I} = \text{Input, O} = \text{Output, A} = \text{Analog.}$

Table 10: LXT974A and LXT975A LED Indicator Signal Descriptions

| Pin# <sup>2</sup>  | Symbol                               | Type <sup>1</sup> | Signal Description <sup>3</sup>                                                                                                                                                                                                                                                                         |

|--------------------|--------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11<br>8<br>4<br>1  | LED0_0<br>LED1_0<br>LED2_0<br>LED3_0 | OD                | <b>LED0 - Ports 0 - 3</b> . In default mode, active Low output indicates transmitter active. However, LED0 is programmable and may also be set to indicate receiver active, link status or duplex status. Refer to LED Configuration Register, Table 51 on page 62, for details on programming options. |

| 12<br>9<br>5<br>2  | LED0_1<br>LED1_1<br>LED2_1<br>LED3_1 | OD                | <b>LED1 - Ports 0 - 3</b> . In default mode, active Low output indicates receiver active. However, LED1 is programmable and may also be set to indicate link status, duplex status, or operating speed. Refer to LED Configuration Register, Table 51 on page 62, for details on programming options.   |

| 13<br>10<br>6<br>3 | LED0_2<br>LED1_2<br>LED2_2<br>LED3_2 | OD                | <b>LED2 - Ports 0 - 3</b> . In default mode, active Low output indicates link up. However, LED2 is programmable and may also be set to indicate duplex status, operating speed or collision. Refer to LED Configuration Register, Table 51 on page 62, for details on programming options.              |

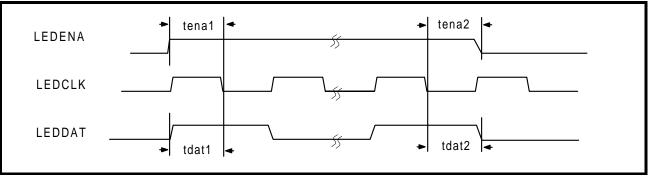

| 17                 | LEDENA                               | О                 | <b>LED Enable.</b> Active High output signals external device that LEDDAT is active.                                                                                                                                                                                                                    |

| 15                 | LEDCLK                               | О                 | LED Clock. 25 MHz clock for LED serial data output.                                                                                                                                                                                                                                                     |

| 16                 | LEDDAT                               | O                 | <b>LED Data.</b> Serial data output for 24 LEDs (6 x 4 ports) data.                                                                                                                                                                                                                                     |

<sup>1.</sup> Type Column Coding: I = Input, O = Output, OD = Open Drain.

<sup>3.</sup> The LXT974A/975A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

<sup>2.</sup> The LXT974A/975A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

<sup>2.</sup> Unused pins should be tied Low.

**Table 11: LXT974A Power Supply Signal Descriptions**

| Pin#                           | Symbol | Туре | Signal Description                                                                                                          |

|--------------------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------|

| 22, 60, 96                     | VCC    | -    | Power Supply. +5V supply for all digital circuits.                                                                          |

| 40, 78                         | VCCMII | -    | <b>MII Supply.</b> +3.3V or +5V supply for MII. A decoupling capacitor to digital ground should be supplied for these pins. |

| 7, 14, 39, 56, 59, 77, 95, 160 | GND    | -    | Digital Ground. Ground return for digital supply.                                                                           |

| 21                             | GNDA   | -    | Analog Ground. Ground return for analog supply.                                                                             |

| 108                            | GNDH   | -    | <b>Ground.</b> Ground return for core analog circuitry.                                                                     |

| 107                            | VCCH   | -    | <b>Supply.</b> +5V supply for core analog circuitry.                                                                        |

| 128, 137, 147, 156             | VCCT   | -    | <b>Transmit Power Supply.</b> +5V supply for transmit circuits.                                                             |

| 127, 136, 146, 155             | GNDT   | -    | Transmit Ground. Ground return for transmit supply.                                                                         |

| 125, 134, 144, 153,            | VCCR   | -    | <b>Receive Power Supply.</b> +5V supply for all receive circuits.                                                           |

| 121, 122, 131, 141, 150        | GNDR   | -    | Receive Ground. Ground return for receive supply.                                                                           |

**Table 12: LXT975A Power Supply Signal Descriptions**

| Pin#                              | Symbol | Туре | Signal Description                                                                                                          |

|-----------------------------------|--------|------|-----------------------------------------------------------------------------------------------------------------------------|

| 22, 60, 96                        | VCC    | -    | <b>Power Supply.</b> +5V supply for all digital circuits.                                                                   |

| 40, 78                            | VCCMII | -    | <b>MII Supply.</b> +3.3V or +5V supply for MII. A decoupling capacitor to digital ground should be supplied for these pins. |

| 7, 14, 39, 56, 59, 77, 95, 160    | GND    | -    | Digital Ground. Ground return for digital supply.                                                                           |

| 21                                | GNDA   | -    | Analog Ground. Ground return for analog supply.                                                                             |

| 108                               | GNDH   | -    | <b>Ground.</b> Ground return for core analog circuitry.                                                                     |

| 107                               | VCCH   | -    | <b>Supply.</b> +5V supply for core analog circuitry.                                                                        |

| 128, 135, 147, 154                | VCCT   | -    | <b>Transmit Power Supply.</b> +5V supply for transmit circuits.                                                             |

| 127, 134, 146, 153                | GNDT   | -    | Transmit Ground. Ground return for transmit supply.                                                                         |

| 125, 132, 144, 151,               | VCCR   | -    | <b>Receive Power Supply.</b> +5V supply for all receive circuits.                                                           |

| 121, 122, 131, 137, 141, 150, 156 | GNDR   | -    | Receive Ground. Ground return for receive supply.                                                                           |

## **FUNCTIONAL DESCRIPTION**

## Introduction

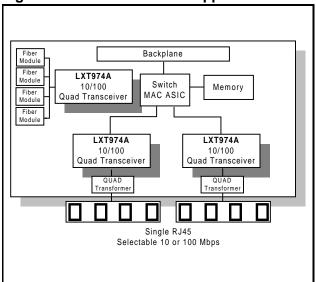

The LXT974A and LXT975A are four-port Fast Ethernet 10/100 Transceivers that support 10 Mbps and 100 Mbps networks. They comply with all applicable requirements of IEEE 802.3. Each port can directly drive either a 100BASE-TX line (>130 meters) or a 10BASE-T line (>185 meters). Figure 3 shows the LXT974A in a typical switch application.

Figure 3: LXT974A Switch Application

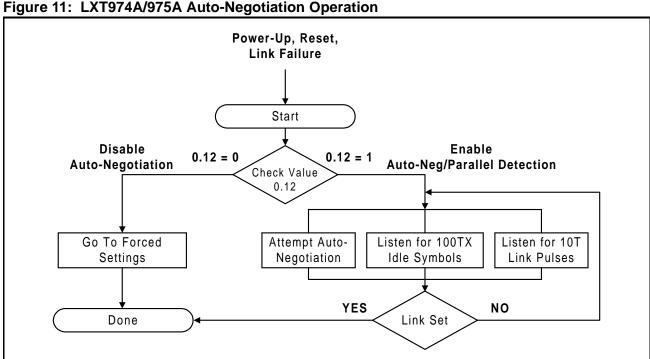

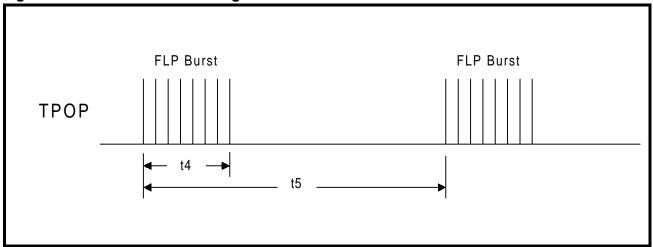

On power-up, the LXT974A/975A uses auto-negotiation/parallel detection on each port to automatically determine line operating conditions. If the PHY device on the other side of the link supports auto-negotiation, the LXT974A/975A will auto-negotiate with it using Fast Link Pulse (FLP) Bursts. If the PHY partner does not support auto-negotiation, the LXT974A/975A will automatically detect the presence of either link pulses (10 Mbps PHY) or Idle symbols (100 Mbps PHY) and set its operating conditions accordingly.

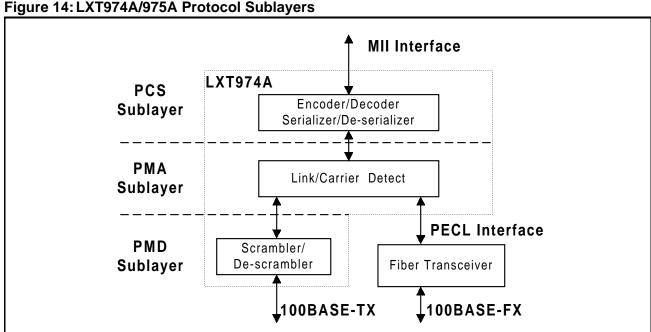

The LXT974A/975A interfaces to four 10/100 Media Access Controllers (MAC)s through the MII interfaces. It performs all functions of the Physical Coding Sublayer (PCS) and Physical Media Attachment (PMA) sublayer as defined in the IEEE 802.3 100BASE-X specification. This device also performs all functions of the Physical Media Dependent (PMD) sublayer for 100BASE-TX connections. The MII speeds are automatically set once port operating conditions have been determined.

The LXT974A/975A provides half-duplex and full-duplex operation at 100 Mbps and 10 Mbps. It also offers standard Loopback Mode for switch applications. The LXT974A/975A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an "X.Y" notation, where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

The LXT975A is pin compatible with the LXT974A except for the network ports. Each port on the LXT974A provides a combination twisted-pair or PECL interface for a 10/100BASE-TX or 100BASE-FX connection.

The LXT975A is optimized for stacked RJ45 modular applications as shown in Figure 4. Ports 1 and 3 support the PECL interface for fiber connections and all four ports support the twisted-pair interface for 10/100BASE-TX connections.

Figure 4: LXT975A Switch Application

# Network Media / Protocol Support

The LXT974A/975A supports both 10BASE-T and 100BASE-TX Ethernet over twisted-pair, or 100 Mbps Ethernet over fiber media (100BASE-FX). A Media Independent Interface (MII) is used for communication with the Media Access Controller (MAC).

## 10/100 Mbps Network Interface

Each of the four network interface ports consists of four external pins (two differential signal pairs). The pins are shared between twisted-pair (TP) and fiber. Signal assignments (input or output, positive or negative) vary depending on whether the port is configured for TP or fiber media. Refer to Tables 1 through 6 for specific pin assignments.

The LXT974A/975A output drivers generate either 100BASE-TX, 10BASE-T, or 100BASE-FX output. When not transmitting data, the LXT974A/975A generates 802.3-compliant link pulses or idle code. Input signals are decoded either as a 100BASE-TX, 100BASE-FX, or 10BASE-T input, depending on the mode selected. Autonegotiation/parallel detection or manual control is used to determine the speed of this interface.

#### Twisted-Pair Interface

When operating at 100 Mbps, MLT3 symbols are continuously transmitted and received. When not transmitting data, the LXT974A/975A generates "IDLE" symbols.

During 10 Mbps operation, Manchester-encoded data is exchanged. When no data is being exchanged, the line is left in an idle state.

In 100 Mbps mode, the LXT974A/975A is capable of driving a 100BASE-TX connection over 100 $\Omega$ , Category 5, Unshielded Twisted Pair (UTP). A 10BASE-T connection can be supported using 100 $\Omega$  Category 3, UTP.

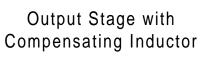

Only a transformer (1:1 on receive side, 2:1 on transmit side), load resistors, and bypass capacitors are needed to complete this interface. Using Level One's patented waveshaping technology, the transmitter predistorts the outgoing signal to reduce the need for external filters for EMI compliance.

A  $4k\Omega$  passive load is always present across the twisted-pair inputs. When enabled, the twisted-pair inputs are actively biased to approximately 2.8V.

#### **Fiber Interface**

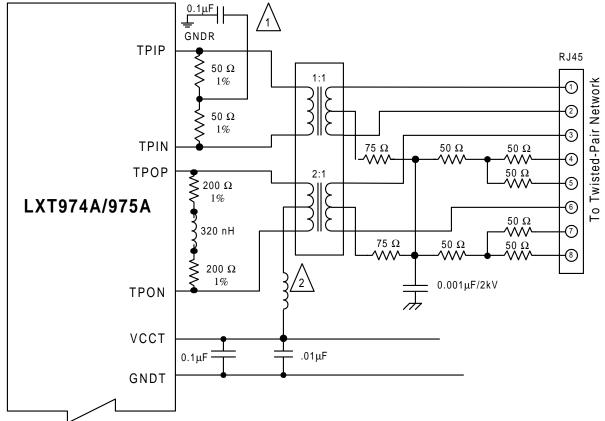

The LXT974A/975A provides a PECL interface that complies with the ANSI X3.166 specification. This interface is suitable for driving a fiber-optic coupler.

The twisted-pair pin assignments are remapped to support the PECL interface. The LXT974A supports both the twisted-pair and fiber interface on all four ports. The LXT975A, optimized for TP operation with dual-high RJ45 connectors, provides dual interfaces on ports 1 and 3.

During 100BASE-FX operation, the FIBI pins receive differential PECL signals and the FIBO pins produce differential PECL output signals.

Fiber ports cannot be enabled via auto-negotiation; they must be enabled via the Hardware Control Interface or MDIO registers.

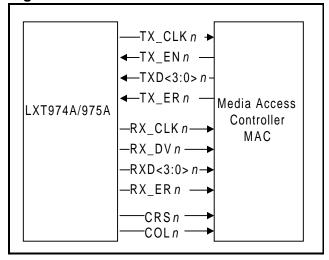

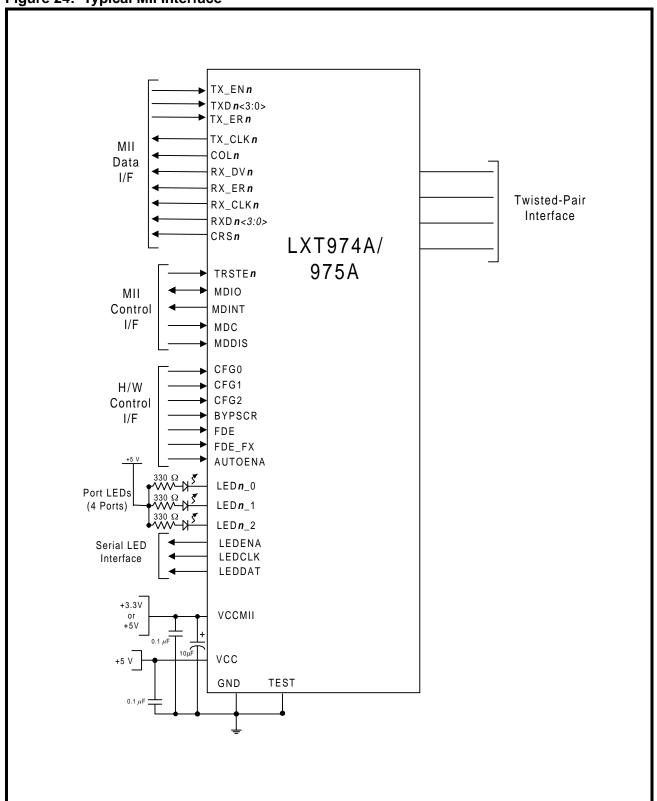

#### **MII Interface**

The LXT974A/975A supports four standard MIIs (one per port). This interface consists of a data interface and a management interface. The MII Data Interface passes data between the LXT974A/975A and one or more Media Access Controllers (MACs). Separate signals are provided for transmit and receive. This interface operates at either 10 Mbps or 100 Mbps. The speed is set automatically, once the operating conditions of the network link have been determined.

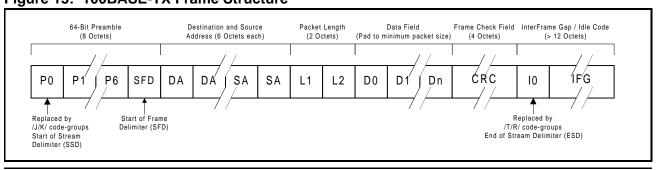

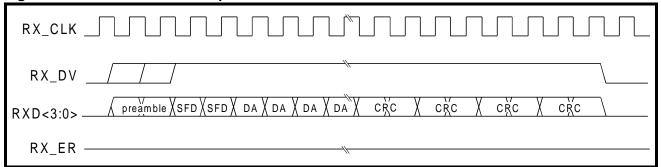

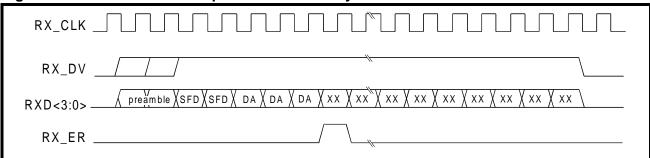

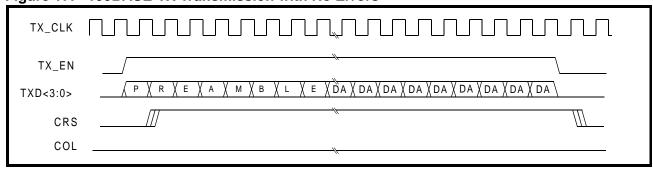

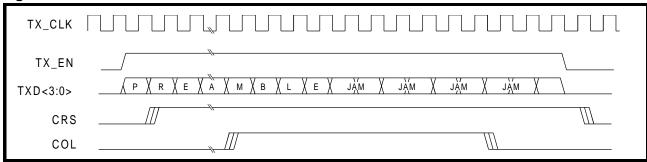

Nine signals are used to pass received data to the MAC: RXD<3:0>, RX\_CLK, RX\_DV, RX\_ER, COL and CRS. Seven signals are used to transmit data from the MAC: TXD<3:0>, TX\_CLK, TX\_EN, and TX\_ER.

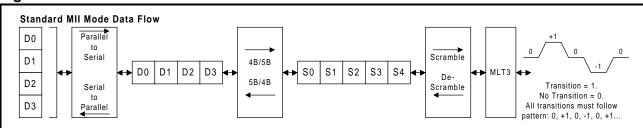

#### **MII Data Interface**

Figure 5 shows the data portion of the MII interface. Separate channels are provided for transmitting data from the MAC to the LXT974A/975A (TXD), and for receiving data (RXD) from the line.

Each channel has its own clock, data bus, and control signals. The LXT974A/975A supplies both clock signals as well as separate outputs for carrier sense and collision. Data transmission across the MII is implemented in 4-bit-wide nibbles.

#### Tristating the MII

The LXT974A/975A asserts RX\_DV, RXD, RX\_CLK and RX\_ER as soon as it receives a packet from the network. When TRSTEn is High, the associated port output signals are tristated.

Figure 5: MII Data Interface

#### **Transmit Clock**

The LXT974A/975A is the master clock source for data transmission. The LXT974A/975A automatically sets the speed of TX\_CLK to match port conditions. If the port is operating at 100 Mbps, TX\_CLK will be set to 25 MHz. If the port is operating at 10 Mbps, TX\_CLK will be set to 2.5 MHz. The transmit data and control signals must always be synchronized to TX\_CLK by the MAC. The LXT974A/975A normally samples these signals on the rising edge of TX CLK.

However, Advanced TX\_CLK Mode is available by setting MII register bit 19.5=1. In this mode, the LXT974A/975A samples the transmit data and control signals on the falling edge of TX\_CLK. When operating under MDIO Control, the user can advance the transmit clock relative to TXD<3:0> and TX\_ER. When Advance TX\_CLK Mode is selected, the LXT974A/975A clocks TXD data in on the falling edge of TX\_CLK, instead of the rising edge. This mode provides an increase in timing margins of TXD, relative to TX\_CLK. Advance TX\_CLK Mode is enabled when bit 19.5 = 1.

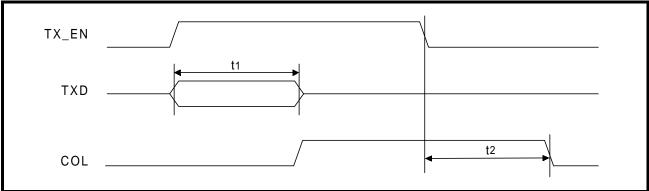

#### **Transmit Enable**

The MAC must assert TX\_EN the same time as the first nibble of preamble, and de-assert TX\_EN after the last bit of the packet.

#### Receive Data Valid

The LXT974A/975A asserts RX\_DV when it receives a valid packet. Timing changes depend on line operating speed:

- For 100TX and 100FX links, RX\_DV is asserted from the first nibble of preamble to the last nibble of the data packet.

- For 10BT links, the entire preamble is truncated. RX\_DV is asserted with the first nibble of the Start of Frame Delimiter (SFD) "5D" and remains asserted until the end of the packet.

#### **Error Signals**

Whenever the LXT974A/975A receives an errored symbol from the network, it asserts RX\_ER and drives "1110" on the RXD pins.

When the MAC asserts TX\_ER, the LXT974A/975A will drive "H" symbols out on the line.

#### **Carrier Sense**

Carrier sense (CRS) is an asynchronous output. It is always generated when a packet is received from the line and in some modes when a packet is transmitted.

On transmit, CRS is asserted on a 10 Mbps or 100 Mbps half-duplex link. Carrier sense is not generated on transmit when the link is operating in full-duplex mode.

Usage of CRS for Interframe Gap (IFG) timing is *not* recommended for the following reasons:

- De-assertion time for CRS is slightly longer than assertion time. This causes IFG intervals to appear somewhat shorter to the MAC than it actually is on the wire.

- CRS de-assertion is not aligned with TX\_EN deassertion on transmit loopbacks in half-duplex mode.

#### **Operational Loopback**

Operational loopback is provided for 10 Mbps half-duplex links when bit 19.11 = 0. Data transmitted by the MAC will be looped back on the receive side of the MII. Operational loopback is not provided for 100 Mbps links, full-duplex links, or when 19.11 = 1.

#### **Test Loopback**

A test loopback function is provided for diagnostic testing of the LXT974A/LXT975A. During test loopback, twisted-pair and fiber interfaces are disabled. Data transmitted by the MAC is internally looped back by the LXT974A/975A and returned to the MAC.

Test loopback is available for 100TX, 100FX, and 10T operation. Test loopback is enabled by setting bit 0.14 = 1, bit 0.8 = 1 (full-duplex), and bit 0.12 = 0 (disable auto-negotiation). The desired mode of operation for test loopback is set using bits 0.13 and 19.2 as shown in Table 13. Loopback paths for the three modes of operation are shown in Figure 6.

**Table 13: Test Loopback Operation**

| Bit  |      |  |  |  |  |

|------|------|--|--|--|--|

| 19.2 | 0.13 |  |  |  |  |

| 0    | 0    |  |  |  |  |

| 0    | 1    |  |  |  |  |

| 1    | 1    |  |  |  |  |

|      |      |  |  |  |  |

<sup>1.</sup> Bit 0.14 = 1, bit 0.8 = 1, and 0.12 = 0 must also be set to enable Test Loopback.

Figure 6: Loopback Paths

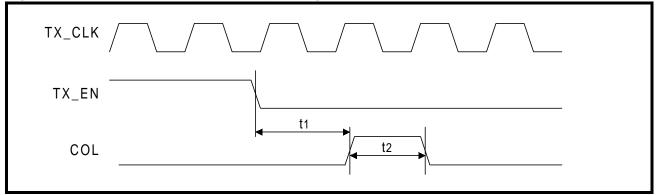

#### Collision

The LXT974A/975A asserts its collision signal, asynchronously to any clock, whenever the line state is half-duplex and the transmitter and receiver are active at the same time. Table 14 summarizes the conditions for assertion of carrier sense, collision, and data loopback signals.

Table 14: Carrier Sense, Loopback, and Collision Conditions

| Speed & Duplex Condition           | Carrier Sense       | Loopback | Collision            |

|------------------------------------|---------------------|----------|----------------------|

| Full-Duplex at 10 Mbps or 100 Mbps | Receive Only        | None     | None                 |

| 100 Mbps, Half-Duplex              | Transmit or Receive | None     | Transmit and Receive |

| 10 Mbps, Half-Duplex, $19.11 = 0$  | Transmit or Receive | Yes      | Transmit and Receive |

| 10 Mbps, Half-Duplex, 19.11 = 1    | Transmit or Receive | None     | Transmit and Receive |

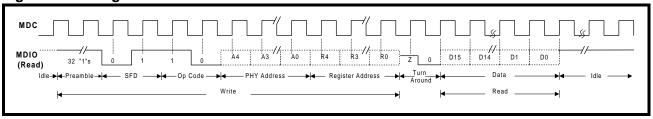

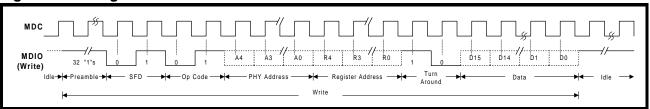

## **MII Management Interface**

The LXT974A/975A supports the IEEE 802.3 MII Management Interface also known as the Management Data Input/Output (MDIO) Interface. This interface allows upper-layer devices to monitor and control the state of the LXT974A/975A. The MDIO interface consists of a physical connection, a specific protocol that runs across the connection, and an internal set of addressable registers. Some registers are required and their functions are defined by the IEEE 802.3 specification. Additional registers are allowed for expanded functionality. The LXT974A/975A is configured with both sets of registers.

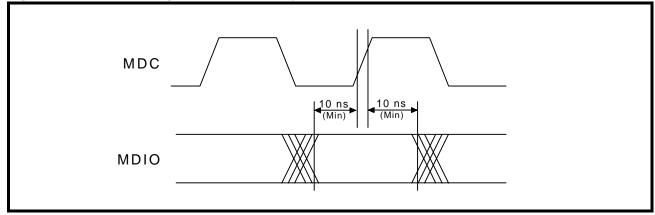

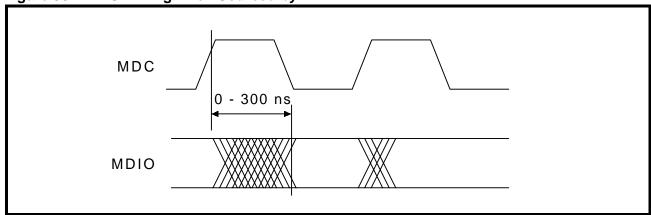

The physical interface consists of a data line (MDIO) and clock line (MDC). Operation of this interface is controlled by the MDDIS input pin. When MDDIS is High, the MDIO operates as a read-only interface. When MDDIS is Low, both read and write are enabled. The timing for the MDIO Interface is shown in Table 40 on page 53. The protocol is shown in Figures 7 and 8 (read and write). The protocol allows one controller to communicate with up to eight LXT974A/975A chips. Bits A4:2 of the 5-bit PHY address are assigned as the LXT974A/975A address. Bits A1:0 are assigned as port addresses 0 through 3. The LXT974A/975A supports 12 internal registers per port (48 total), each of which is 16 bits wide.

Figure 7: Management Interface - Read Frame Structure

Figure 8: Management Interface - Write Frame Structure

#### **MII Interrupts**

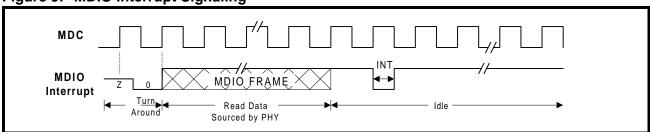

The LXT974A/975A provides interrupt signals in two ways. The MDIO interrupt reflects the interrupt status of each port addressed by the read. Details are shown in Figure 9.

Setting bit 17.1 = 1 on all four ports, enables global interrupts using the MDINT pin. An active Low on this pin indicates a status change on the LXT974A/975A. Interrupts may be caused by:

- · Link status change

- · Auto-negotiation complete

- Full-duplex status change

- Jabber detect

Figure 9: MDIO Interrupt Signaling

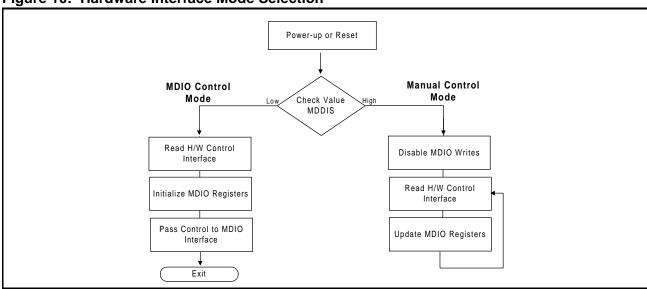

#### **Hardware Control Interface**

The Hardware Control Interface is used to configure operating characteristics of the LXT974A/975A. When MDDIS is Low, this interface provides initial values for the MDIO registers, and then passes control to the MDIO Interface. When MDDIS is High, this interface provides continuous control over the LXT974A/975A.

Individual chip addressing allows multiple LXT974A/975A devices to share the MII in either mode. Tables 15 through 17 show how to set up the desired operating configurations using the Hardware Control Interface.

Table 15: Configuring the LXT974A/975A via Hardware Control

| Desired Configuration                                    | Pin Name            | Input Value | MDIO Registers |

|----------------------------------------------------------|---------------------|-------------|----------------|

| Auto-Negotiation Enabled on all ports <sup>1, 2, 3</sup> | AUTOENA             | High        | 0.12 = 1       |

|                                                          | $SD/\overline{TP}n$ | Low         | 19.2 = 0       |

| Auto-Negotiation Disabled on all ports <sup>4</sup>      | AUTOENA             | Low         | 0.12 = 0       |

| Scrambler Bypassed on all ports                          | BYPSCR              | High        | 19.3 = 1       |

| Scrambler Enabled on all ports                           | BYPSCR              | Low         | 19.3 = 0       |

- 1.  $SD/\overline{TP}n$  must be set Low for Auto-Negotiation operation.

- 2. Refer to Table 16 for Hardware Control Interface functions advertised when auto-negotiation is enabled.

- 3. Fiber operation can be forced *per port* via SD/TPn pins when auto-negotiation is enabled. See Table 17 for details.

- 4. Refer to Table 17 for Hardware Control Interface functions available when auto-negotiation is disabled.

Table 16: Configuring LXT974A/975A Auto-Negotiation Advertisements Via Hardware Control

| Desired -<br>Configuration <sup>1,2</sup> |                      | Pi              | MDIO Registers    |                   |                             |     |     |     |     |

|-------------------------------------------|----------------------|-----------------|-------------------|-------------------|-----------------------------|-----|-----|-----|-----|

|                                           | SD/TPn<br>(per port) | FDE<br>(global) | CFG_2<br>(global) | CFG_1<br>(global) | CFG_0 <sup>3</sup> (global) | 4.5 | 4.6 | 4.7 | 4.8 |

| Advertise All                             | Low                  | Ignore          | Low               | Low               | Ignore                      | 1   | 1   | 1   | 1   |

| Advertise 100 HD                          | Low                  | Low             | High              | Low               | Ignore                      | 0   | 0   | 1   | 0   |

| Advertise 100 HD/FD                       | Low                  | High            | High              | Low               | Ignore                      | 0   | 0   | 1   | 1   |

| Advertise 10 HD                           | Low                  | Low             | Low               | High              | Ignore                      | 1   | 0   | 0   | 0   |

| Advertise 10 HD/FD                        | Low                  | High            | Low               | High              | Ignore                      | 1   | 1   | 0   | 0   |

| Advertise 10/100 HD                       | Low                  | Low             | High              | High              | Ignore                      | 1   | 0   | 1   | 0   |

- 1. Refer to Table 15 for basic configurations.

- 2. Refer to Table 17 for Hardware Control Interface functions available when auto-negotiation is disabled.

- Auto-Negotiation is not affected by CFG\_0.

Table 17: Configuring the LXT974A/975A with Auto-Negotiation Disabled